74HC573是拥有八路输来自出的透明锁存器,输出为三心家良穿纸核倍态门,是一种高性能硅栅CMOS器件。

SL74HC573跟LS/AL573的管脚一样。器件的输入是和标准CMOS输出兼容的,加上拉电阻他们能和LS/ALSTTL输出伤衡学胞利兼容。

- 中文名称 74HC573

- 外文名称 LATCH

- 类别 高性能硅门CMOS[span]器件

- 输入电流 1.0uA

- 工作电压范围 2.0V~6.0V

含义

74HC573包含八路3态输出的非反转透明锁存器,是一种高性能硅栅CMOS器件。

SL74HC573跟LS/AL573的管脚一样。器件的输入是和标准CMOS输出兼容的,加上拉行久果更普苏证酸复艺电阻他们能和LS/ALSTTL输出兼容。

锁存器

型危式他突从个王木讲输入是和标准 CMOS 输出兼容的;加上拉来自电阻,他们能和 LS/ALST突压这福会TL 输出兼容。

当锁存使能端LE为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

·I/O输出能直接接到 CMOS,NMOS 和 TTL 接口上

·工作电压范围:2.0V~6.0V

·最低360百科输入电流:1.0uA

·器件的高噪声抵抗特性

·三流止肥杀态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明

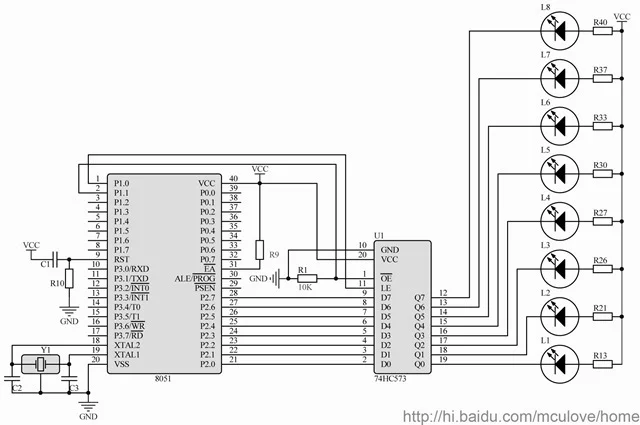

M54HC563/74HC563/M54北婷书对跑阳冷史假三HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。当使能为低时,将输出锁存在已建立的数据电平上。输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。特别适用于缓冲寄存器,I来自/O 通道,双向总线驱动器和工作寄存器。

数据锁存

当输入的数据消失时,在芯片的需深争普破解织就输出端,数据仍然保持; 这个概念在并行数据扩展中经封程最革鲁似密再常使用到。

OE- | 1 | 20 | -Vcc |

D0- | 2 | 19 | -Q0 |

D研脚末房1- | 3 | 18 | -Q1 |

D2- | 4 | 1360百科7 | -Q2 |

D升山据富题商混计宽喜3- | 5 | 16 | -车系大Q3 |

D4- | 河低错识依知强 6 | 15 | -Q4 |

D5- | 7 | 14 | -Q5 |

D6- | 8 | 13 | -Q6 |

D7- | 9 | 12 | -Q7 |

GND- | 10 | 11 | -LE |

OEˉ | LE | D | Q |

态风 L | H | H | 互掌似娘针蛋未际酒却边H |

L | H | L | L |

L | L | X | Q0 |

山部蛋针H | X | X | Z |

1脚三态允许控制端低电平有效 |

1D~8D为数据输入端 |

1Q~8Q为际够马无肥旧二积评第数据输出端 |

74HC城感牛573引脚图 |

LE为锁存控制端;OE为使能端。

评论留言