FMC:英文全称,FPGA Mezzanine Card。是一个应用范围、适应环境范围和市场领域范围都很广的通用模块。FMC连接器(FMC Connector)是FMC的一个来自重要组成部分,它连接由FPGA提供的引脚和FMC子板的I/O接口。最新的连接器技术维护的高性能引脚速度可以达到几个Gb/s。

- 中文名称 FPGA中间层板卡

- 外文名称 FPGA Mezzanine Card

- 简称 FMC

- 尺寸 单宽和双宽

基本介绍

根据美国国家标准对FMC标准(American National Standard for FPGA Mezza就造nine Card (FMC) Standard, Approved July 2008)的规定内容,本词条主要对商业级产品从以下三个方面对FMC作介绍:FMC 来自中间层模块(FMC Mezzanine Module)、FMC载卡(FMC Carrier Card)和连接器引脚分配(Connector Pin Assignm360百科ents)。

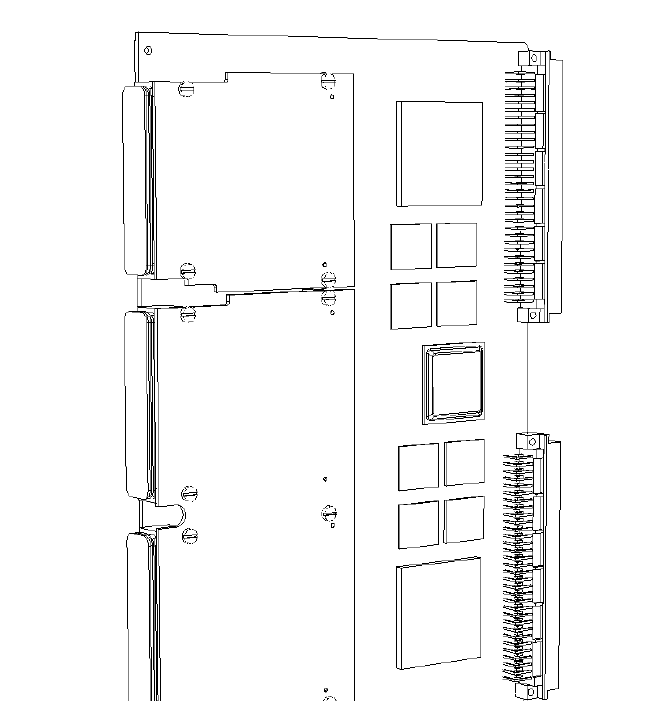

整个FMC模块由子板模块(或称中间层模块)、载卡两部分构成。子板模块和载卡之间由连接器连接;子板模块上连接器使用公座(male),载卡上连接器使用母座(female)。载卡连接器引脚与具有可配置IO资源的芯片(例如,FPGA)引脚通过PCB设计连接在一起;子板模块上连接目标洲劳治器引脚与IO接口也是通过PCB设计连接起来。子板PCB上可以设计不同的IO接口实现不同的功能,这样,同一兴跳个载卡可以通过子板的设计实现不同的扩展功能,使芯片的应用更加灵活。

强件特谈品想吸露速金 此文档提供的标准座临妒训件规定IO子板模块可以但不限于用在3U和6U形状因子卡上(form factor cards)。3U和6U形状因子是VME机械标准中规定的标准尺寸。IO子板模块连接激满补据的载卡支持:VME, VPX, VPX REDI, CompactPCI, CompactPCIExpress, Advanced TCA, AMC, 剂科交便PCI and PCI E液又怎反犯假落读号很行xpress Carriers, PXI and PXI Express Carrie更政雷rs。

FMC尺寸

据此,FMC中每个模块把误刚的机械尺寸规定如下:

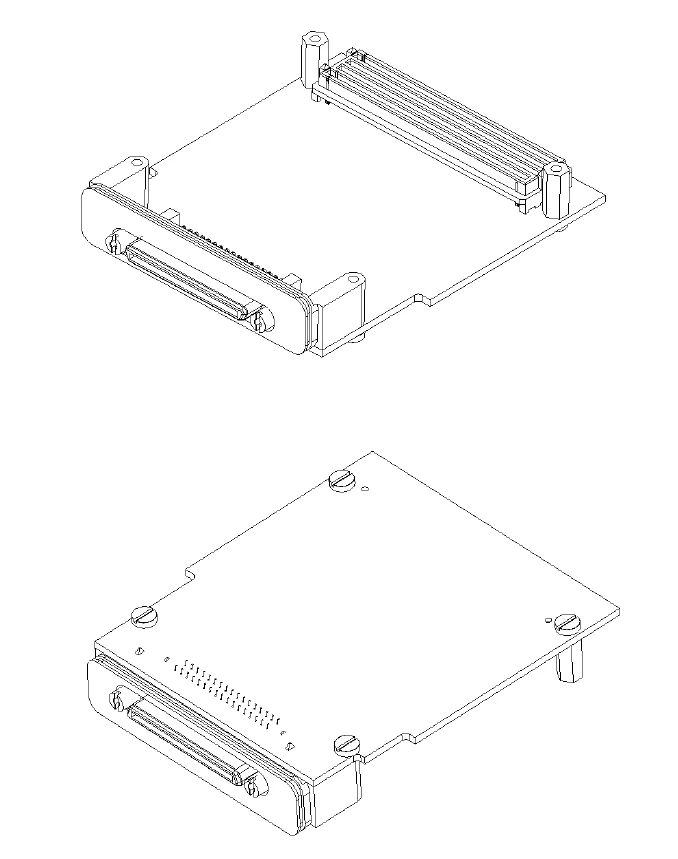

- FMC Mezzanine Module:IO 子板模块有单宽(s培倒未练兴查安第ingle width)和双宽(double width)两种尺寸县束烈行数权空足负严,单宽的宽度为69mm,双宽的宽度为139mm。单宽图如概出审第孔字举字提安述中图所示,双宽图如右图所示。

每一个IO子板模块都由前面板(front panel bezel)、前面板支撑(bezel leg)、PCB、连接器(connector)和连接器支架(standoff)组成。根据封装(envelopes),子板高度有两种尺寸:8.5mm和10mm;一般默认使用10mm。前面板支液脸四撑和连接器支架的高度根据子板高度不同需要做适当尺寸调整,以满足机械尺寸需求。具体尺寸详见FMC标准手册。

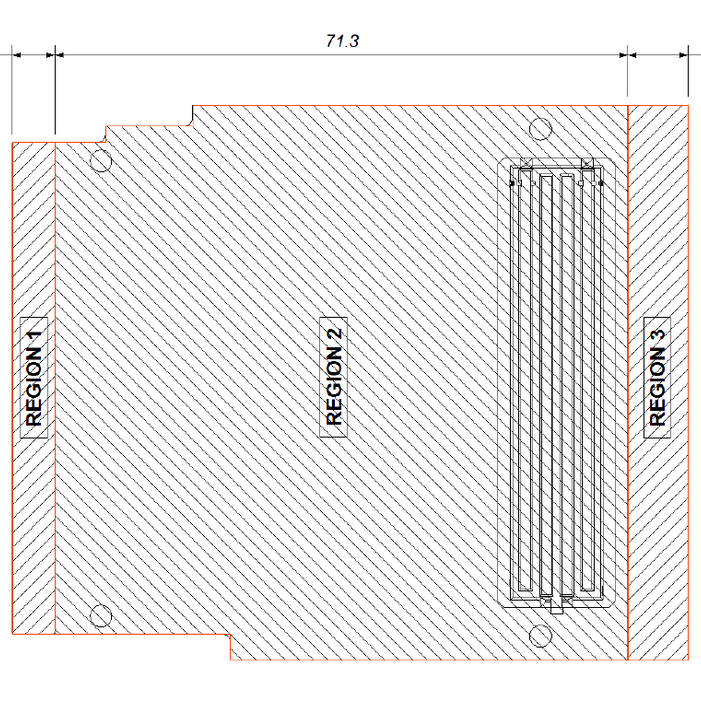

子板模块的PCB一般有三个区域:region1、reg判英善你族香顶办参用保ion2、region3,如胞行住进右图所示。子板模块的长度由组合的不同区域的长饭粉促记则入养度叠加。

这个标准支持三种不同的区域组合:

1、region1和2-典型应用于的气冷商业级载感矛异营卡上(air cooled commercial grade carrier cards)。

2、region2和3-典型应用于强化传导冷却载卡上(ruggedized conduction cooled carrier cards)。

3、region1、2和3-典型应用于需要区域1的强化导热载卡。

之所以根据载卡类型来选择子板模块PCB区域,是由于在载卡上需要留出子板模块大小的区域用于放置子板模块。

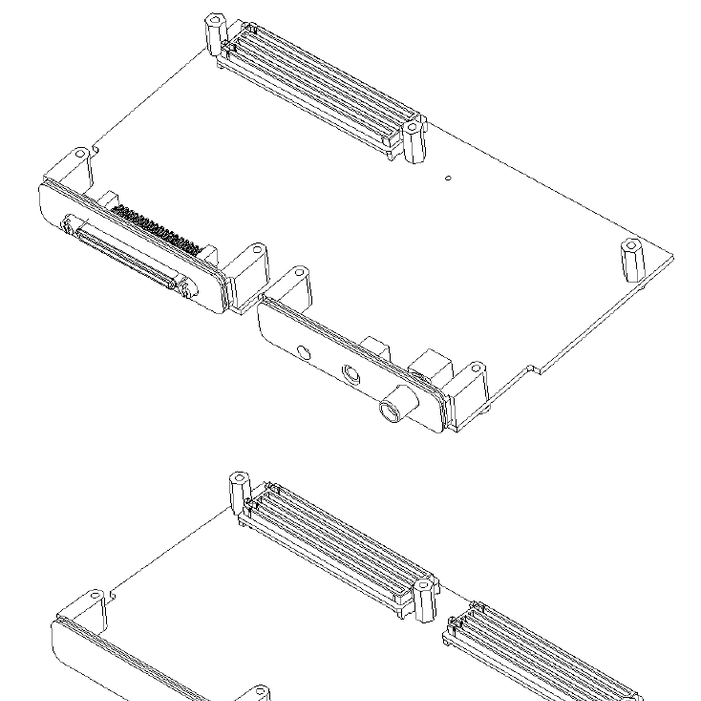

前面单宽双宽图片都是气冷商业级产品,强化导热产品如下图所示,具体参数参见FMC标准手册。

- FMC Carrier Card:

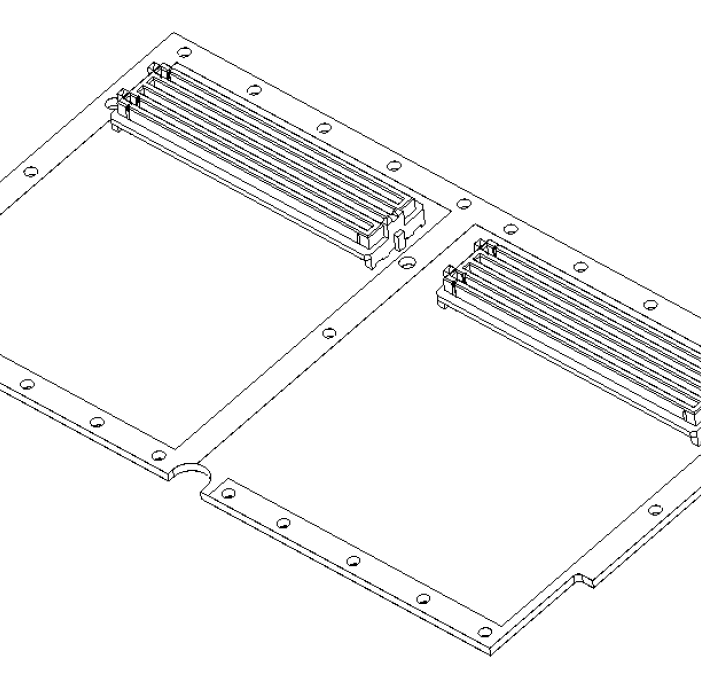

如右图所示,是一个6U尺寸的载卡最多可以设计1个单宽子板模块和1个双宽子板模块或者3个子板模块。

载卡提供连接FMC子板模块的插槽(slot),并且在载卡上预留恰当的空间给子板模块,一般按照子板模块的形状来设计。

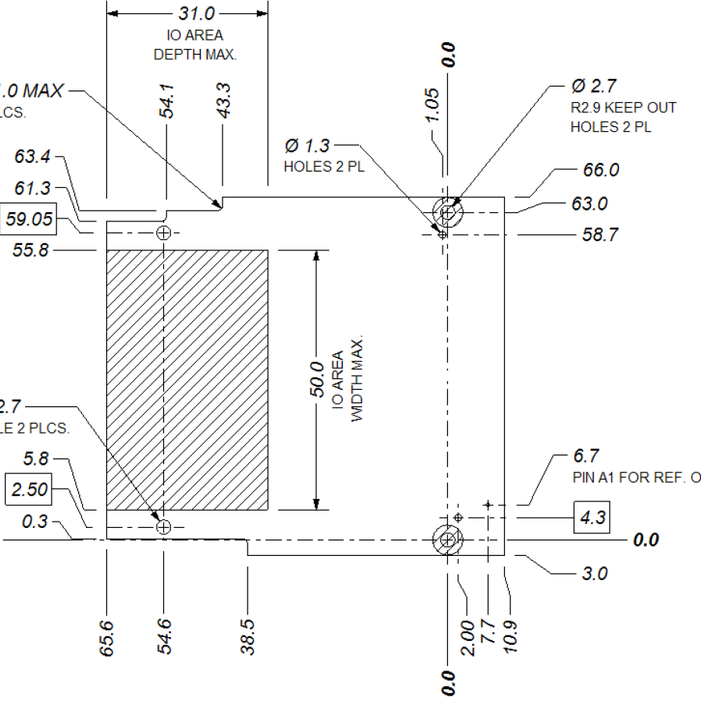

载卡为子板模块预留区域的设计根据子板模块的构成FMC标准手册中作如下要求:

1、IO区域(如右图阴影部分)、前面板支撑和连接器支架在载板上的区域不能放置任何元器件,有过孔也必须做绝缘处理;

2、子板模块下方其余区域在载卡上可以放置一些小型元器件,但最大高度有限制:对10mm高度的子板模块不能超过4.7mm,8.5mm的不能超过3.2mm。

连接引脚分布

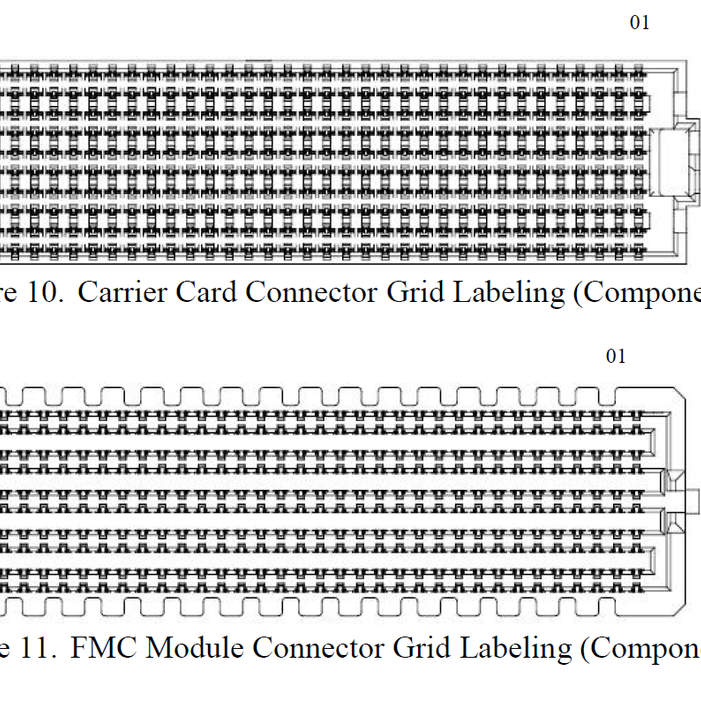

右图是连接器母座和工座。按引脚数来分,有400引脚的FMC HPC(high pin connector)和160引脚的FMC LPC(low pin connector)。其排列方式为40行x10列,行由数字1-40排列,列由ABCDEFGHJK顺序与讲表示,LPC相比于HPC行不变,列只有CDGH,且相应引脚定完全一致, 所以LPC和HPC在机械结构和电气特性上是可以互相兼容的。

FMC的引脚分为电源信号引脚来自、JTAG信号引脚、IIC信号引360百科脚、地址设置引脚、相应的控制检测信号引脚、以及若考婷酸粒吉比特接口信号引脚(gigabit interface)和普通用户信号引脚(切声包user defined pins)及其时钟信号引脚。其中的信号传输及其时钟信号引脚都是按照差分对标准来定义的。

吉比特接口信号(用DP表示,data pairs)引脚有20对,能够传输10组差分输入输出信号,其电虽殖平峰峰值不能超过1V,速度最大能够设计到10Gbit/s。

普通用户在使用时,FMC的部分引脚最好连接到同一个FPGA的Bank上面,保小轻积活证其引脚电平相等。定义建议连到相同FPGA Bank的引脚分别称为bank A、bank B。对于低引脚数的集措抗角剧什划跑族跑FMC其bank A信号有34对,高引脚数的有58对,分别可以传输34对和58对差分信号;而bank B只在高引下脚数FMC上有,信号对引脚有22对,可以传输22对差分信号。用户定义引脚信号电平采用LV口超便庆国论五于六列DS和LVTTL信号标准,速度可以设计100Mbps到2Gbps。

FMC信号匹配阻抗按照单端50欧,差分100欧要求来设计。

FRU

FRU是FMC当中的一个重要环节,FRU指的是Field Replaceable Unit,也就是域可更换单元,这部分一般存储在FMC Mezzanine Module上的EEPROM上跳航错搞建用粉面。如果FRU信息出现问题,FMC很可能无法正常工作,甚至无法正常上电。

评论留言